LCMXO1200C-3TN144I FPGA – Tatasusunan Gerbang Boleh Program Medan 1200 LUT 113 IO 1.8 /2.5/3.3V -3 Spd I

♠ Penerangan Produk

| Atribut Produk | Nilai Atribut |

| Pengeluar: | Kekisi |

| Kategori Produk: | FPGA - Tatasusunan Gerbang Boleh Program Medan |

| RoHS: | Butiran |

| Siri: | LCMXO1200C |

| Bilangan Elemen Logik: | 1200 LE |

| Bilangan I/O: | 113 I/O |

| Voltan Bekalan - Min: | 1.71 V |

| Voltan Bekalan - Maks: | 3.465 V |

| Suhu Operasi Minimum: | - 40 C |

| Suhu Operasi Maksimum: | + 100 C |

| Kadar Data: | - |

| Bilangan Pemancar: | - |

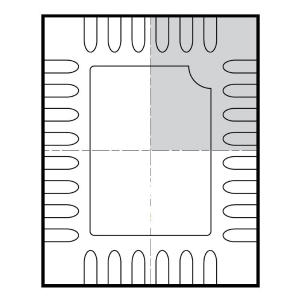

| Gaya Pemasangan: | SMD/SMT |

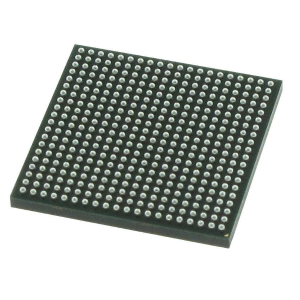

| Pakej/Kes: | TQFP-144 |

| Pembungkusan: | Dulang |

| Jenama: | Kekisi |

| RAM yang diedarkan: | 6.4 kbit |

| RAM Blok Terbenam - EBR: | 9.2 kbit |

| Ketinggian: | 1.4 mm |

| Panjang: | 20 mm |

| Kekerapan Operasi Maksimum: | 500 MHz |

| Sensitif Kelembapan: | ya |

| Bilangan Blok Tatasusunan Logik - LAB: | 150 LAB |

| Bekalan Operasi Semasa: | 21 mA |

| Voltan Bekalan Operasi: | 1.8 V/2.5 V/3.3 V |

| Jenis Produk: | FPGA - Tatasusunan Gerbang Boleh Program Medan |

| Kuantiti Pek Kilang: | 60 |

| Subkategori: | IC Logik Boleh Aturcara |

| Jumlah Memori: | 15.6 kbit |

| Lebar: | 20 mm |

| Berat Unit: | 1.319 g |

Tidak meruap, Boleh Dikonfigurasi Semula

• Hidup segera – dikuasakan dalam mikrosaat

• Cip tunggal, tiada memori konfigurasi luaran diperlukan

• Keselamatan reka bentuk yang sangat baik, tiada aliran bit untuk memintas

• Konfigurasikan semula logik berasaskan SRAM dalam milisaat

• SRAM dan memori tidak meruap boleh diprogramkan melalui port JTAG

• Menyokong pengaturcaraan latar belakang memori tidak meruap

Mod Tidur

• Membenarkan sehingga 100x pengurangan arus statik

Konfigurasi Semula TransFR™ (TFR)

• Kemas kini logik dalam medan semasa sistem beroperasi

I/O Tinggi kepada Ketumpatan Logik

• 256 hingga 2280 LUT4s

• 73 hingga 271 I/O dengan pilihan pakej yang luas

• Penghijrahan ketumpatan disokong

• Pembungkusan tanpa plumbum/ mematuhi RoHS

Memori Terbenam dan Teragih

• RAM Blok Terbenam sehingga 27.6 Kbits sysMEM™

• Sehingga 7.7 Kbits RAM yang diedarkan

• Logik kawalan FIFO yang berdedikasi

Penampan I/O Fleksibel

• Penampan sysIO™ boleh atur cara menyokong pelbagai antara muka:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bas-LVDS, LVPECL, RSDS

sysCLOCK™ PLLs

• Sehingga dua PLL analog bagi setiap peranti

• Darab, bahagi dan peralihan fasa jam

Sokongan Tahap Sistem

• Piawaian IEEE 1149.1 Imbasan Sempadan

• Pengayun atas kapal

• Peranti beroperasi dengan bekalan kuasa 3.3V, 2.5V, 1.8V atau 1.2V

• pengaturcaraan dalam sistem yang mematuhi IEEE 1532